Asus overclocker SkatterBencher published a new video today where he was able to overclock AMD's best CPU for gaming, the Ryzen 7 7800X3D to 5.4GHz, despite the chip's overclocking limitations. He successfully bypassed AMD's 5 GHz ceiling by using external clock generators to overclock the CPU cores.

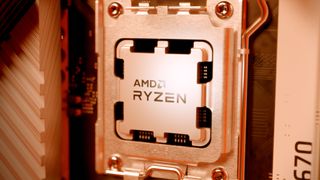

AMD's Ryzen 7 7800X3D is the new gaming champion among PC processors, delivering blisteringly fast gaming performance with the help of 3D V-Cache technology. However, the thermal limitations of the 3D stacking tech have forced AMD to disable manual overclocking on the chip, with the exception of Precision Boost Overdrive or PBO and AMD's Curve Optimizer.

SkatterBencher was able to get around this problem with the help of an Asus ROG Crosshair X670E Hero that has not one, but two external clock generators to aid in overclocking. To achieve 5.4GHz, SkatterBencher used a unique combination of multiple features, including the external clock generator, Precision Boost Overdrive, and AMD's Curve Optimizer to boost clock speeds.

This overclocking strategy is complicated, but the execution is very effective. Precision Boost Overdrive is used to prevent power limitations from occurring on the chip. The external clock generator is used to physically boost clock speeds, and the curve optimizer is used to — not undervolt — but overvolt the chip beyond stock voltages to keep clocks stable.

This led to a 5.4 GHz peak boost on a single core, with a 4.85 GHz boost clock on all eight cores at voltages well under 1.2v. This represents a 7.7% boost to boost frequencies and a 10% boost to single-core clocks compared to stock frequencies.

The overclock is very impressive and shows how much headroom is actually available in some of these chips. Only time will tell how quickly the 7800X3D will degrade with the overvolt applied, but the overclock is impressive nonetheless. With a clock of 5.4 GHz, you effectively have the same compute performance as a standard Ryzen 7 7700X with the additional L3 3DV-Cache to boost gaming performance.